# Audio Engineering Society Convention Paper 7909

Presented at the 127th Convention 2009 October 9–12 New York, NY, USA

The papers at this Convention have been selected on the basis of a submitted abstract and extended precis that have been peer reviewed by at least two qualified anonymous reviewers. This convention paper has been reproduced from the author's advance manuscript, without editing, corrections, or consideration by the Review Board. The AES takes no responsibility for the contents. Additional papers may be obtained by sending request and remittance to Audio Engineering Society, 60 East 42<sup>nd</sup> Street, New York, New York 10165-2520, USA; also see www.aes.org. All rights reserved. Reproduction of this paper, or any portion thereof, is not permitted without direct permission from the Journal of the Audio Engineering Society.

# **The 48 Volt Phantom Menace Returns**

Rosalfonso Bortoni<sup>1</sup> and Wayne Kirkwood<sup>2</sup>

THAT Corporation, Milford, MA, 01757, USA <sup>1</sup><u>rb@thatcorp.com</u> and <sup>2</sup><u>wek@thatcorp.com</u>

#### ABSTRACT

In 2001, Hebert and Thomas presented a paper at the 110<sup>th</sup> AES Convention which described the "phantom menace" phenomenon wherein microphone phantom power faults can damage audio input circuitry. This paper offers new information about the phantom menace fault mechanisms, analyzes common protection circuits, and introduces a new protection scheme that is more robust. In addition, new information is presented relating these input protection schemes to audio performance, and recommendations are made to minimize noise and distortion.

#### 1. INTRODUCTION

In a paper presented at the 110<sup>th</sup> AES Convention, Hebert and Thomas described the "phantom menace," wherein phantom power faults can damage audio input circuitry [1]. Their approach focused on the analysis of a "common mode fault" occurring at the microphone preamplifier inputs, which was described as a "fault at both inputs, simultaneously."

However, this is not the only fault condition that can occur. New fault mechanisms are considered in this paper, and we show that commonly used protection schemes for popular integrated microphone preamplifiers do not always protect the preamplifiers as expected.

The authors named those new fault mechanisms as "single-ended fault" and "differential fault," which are described in this work as "fault at one input, with the other input open," and "fault at one input, with the other input already grounded," respectively.

We focus our analysis on simulated behavior of the THAT 1510 and 1512 [2] IC preamplifiers. The findings presented are based on our extensive experience and bench tests. Most of the principles presented here apply equally well to other IC preamplifiers, such as the Texas Instruments INA217 [3] and INA163 [4], and the Analog Devices SSM2019 [5]. Indeed, many of our findings may be applied to other (discrete) preamplifier designs, particularly those using bipolar junction transistors as input devices.

#### 2. FAULT MECHANISMS

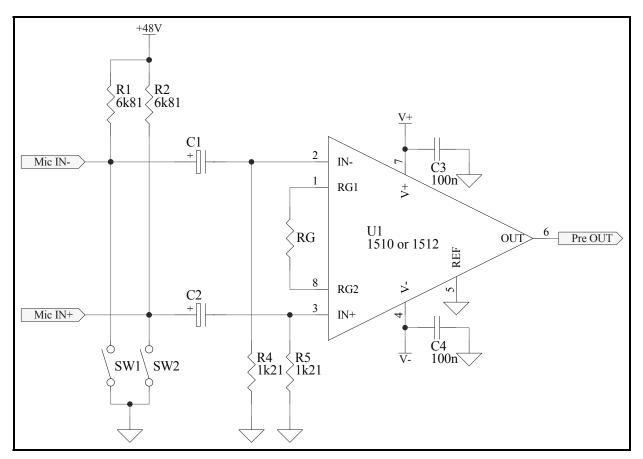

Figure 1 shows, from the perspective of phantom power faults, an unprotected microphone preamplifier using the THAT 1510/1512 with phantom power capability. Phantom power faults are simulated by closing switches SW1 and/or SW2.

Figure 1. Microphone preamplifier with phantom power capability. Switches SW1 and SW2, when properly closed, cause the three fault modes discussed in this paper.

In normal operation, both SW1 and SW2 are open and the differential microphone signal is connected between the junction of R1 and C1, and the junction of R2 and C2. Closing both switches simultaneously simulates the common-mode fault described by Hebert and Thomas. Closing one (or the other) individually while the other switch remains open simulates the "single-ended" fault. Closing the first switch, then the second switch (while the first one remains closed) simulates a "differential" fault.

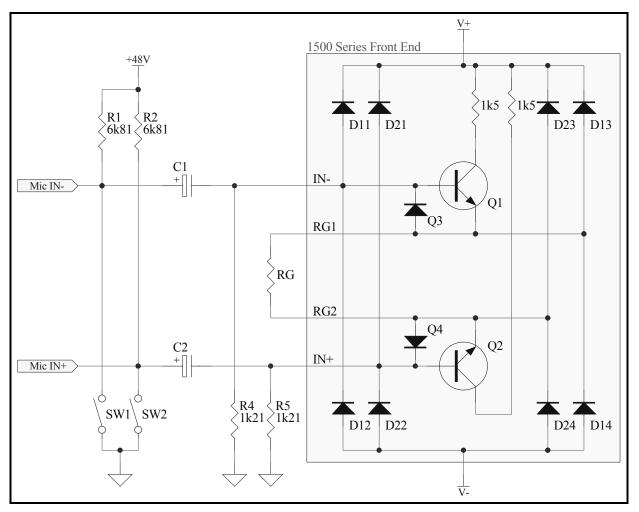

Our analysis was intended to determine the voltages and current paths that appear during each of the fault modes under discussion, as well as the magnitudes of the transient signals. The basic circuit used for simulations is shown in Figure 2.

This circuit includes a THAT 1500-series simplified front end circuit with external gain and bias resistors (RG, R4, and R5, respectively), input coupling capacitors (C1 and C2), and phantom power connections (+48 V and 6.81 k $\Omega$  resistors R1 and R2).

The 1500-series' front end is represented by the input transistors Q1 and Q2, their respective base-emitter reverse-bias protection diodes Q3 and Q4, and internal (ESD protection) diodes D11, D12, D13, D14, D21, D22, D23, and D24 [2].

Simulations of current and voltages flowing in this circuit were made for all three variations of fault conditions, with five different values of input capacitors (C1 and C2). The input capacitors simulated include three commonly used values:  $22 \ \mu\text{F}$ ,  $47 \ \mu\text{F}$ , and  $100 \ \mu\text{F}$ , and two other less-common values:  $220 \ \mu\text{F}$  and  $470 \ \mu\text{F}$ . As might be expected, the duration of the fault currents is much longer with larger input coupling capacitors. The larger capacitors require more energy to be dissipated in the circuit and its protection network [1].

Figure 2. Microphone preamplifier basic input circuit used for simulations.

# 2.1. Common-Mode Fault

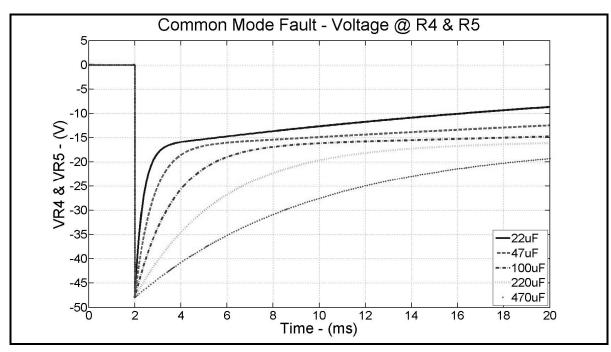

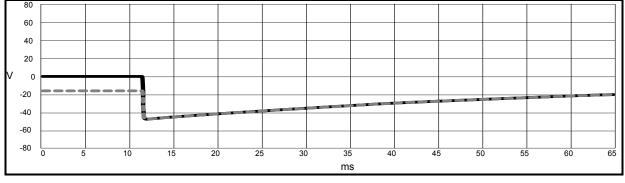

A common-mode fault occurs when both inputs are shorted to ground simultaneously, with phantom power turned on, and without a microphone connected. This fault is simulated by closing switches SW1 and SW2 simultaneously (see Figure 2).

Prior to the fault, both input capacitors, C1 and C2, are charged to +48 V with respect to ground. During the fault both inputs are shorted, simultaneously, to ground. When the positive ends of C1 and C2 are grounded, (the voltage across these capacitors is stored and cannot change instantaneously) -48 V is developed across bias resistors R4 and R5, and appears at the IC inputs IN-

and IN+. This voltage gradually returns to 0 V as the capacitors discharge.

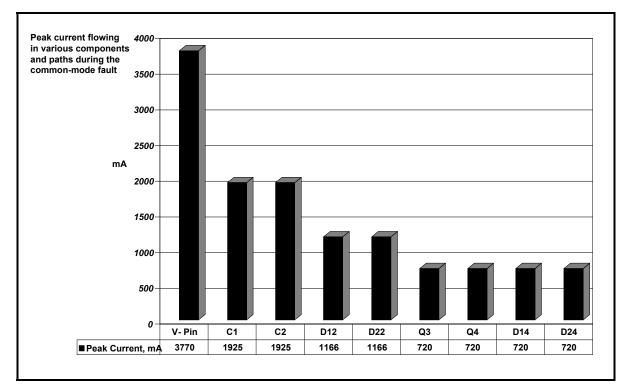

Figure 3 shows an idealized (SPICE) simulation of this voltage vs. time (the fault occurs at t=2ms). This simulation assumes that the supply rails (V+ and V-) for the IC are  $\pm 15$  V. The time it takes for C1 and C2 to discharge is proportional to their value. The simulation shows that after closing SW1 and SW2, the charge on the input capacitors first finds a discharge path to the V-rail through several paths internal to the IC (see Figure 4). The most direct is through electro-static discharge (ESD) protection diodes D12 and D22. Note that it reaches a peak of ~1.2 *Amperes*; the duration of the current spike depends on the size of the input coupling capacitors.

Because this current is so large, and because the diodes D12 and D22 are small devices intended to protect against the smaller energies involved in ESD, the voltage across these components increases to the point that other devices begin to conduct. The charge on C1 also finds its way through Q3 in series with D14, while the charge on C2 finds its way through Q4 in series with D24. Figure 4 shows these currents, which simulation predicts will reach about 720mA.

D14 and D24 are also ESD protection devices, while Q3 and Q4 are intended to protect the input transistors (Q1 and Q2) from having their base-emitter junctions reverse biased to the point that they conduct as zener diodes. (Doing so would harm the low-noise behavior of these devices, thus compromising the noise performance of the preamplifier.) Q3 and Q4 ensure that the baseemitter junctions of Q1 and Q2 never see more than a volt or so in reverse.

Once the voltage at IC pins IN- and IN+ becomes more positive than the negative supply rail (-15 V in the simulation), current no longer flows in the input pins, but shifts to flowing only through R4 and R5. This accounts for the second, longer time constant evident in the 22  $\mu$ F cap curve of Figure 3. There is one exponential discharge to the -15 V rail, based on the time constant formed by the protection diodes and the input coupling capacitors, and then a second to ground based on the time constant formed by the input bias resistors and the input coupling capacitors.

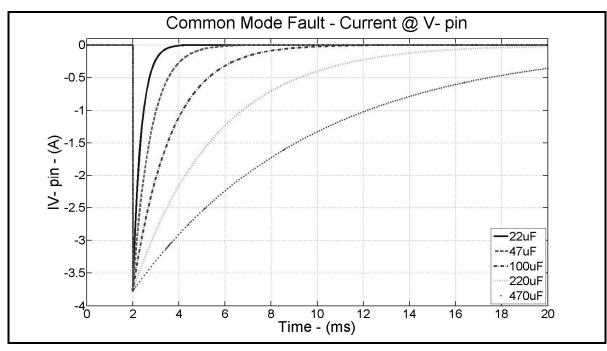

Referring to Figure 5, the currents through the input capacitors C1 and C2 end up flowing into the V- pin of the IC. As shown in Figure 4, each input capacitor delivers currents up to nearly 2 *Amperes*; the total current flowing through the negative power supply pin in the IC is almost 4 A!

For the common-mode fault, no current flows through the base-emitter junctions of input transistors Q1 and Q2 because they are reversed biased during the fault. In addition, no current flows through the gain resistor RG. As well, the fault currents in the input bias resistors R4 and R5 are relatively small (~40 mA peak for 1.21 k $\Omega$  resistors).

Figure 3. Voltage across bias resistors R4 and R5 during the common mode fault, circuit of Figure 2.

AES 127th Convention, New York, NY, USA, 2009 October 9–12

Figure 4. Current distribution during the common mode fault.

Figure 5. Total fault current flowing through the IC (at V- pin).

## 2.2. Single-Ended Fault

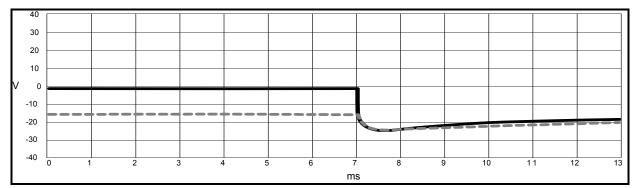

A single-ended fault occurs when only one input is connected to ground with phantom power turned on, and without a microphone connected. This type of fault is simulated by closing one switch in Figure 1, SW1 or SW2, while the other remains open.

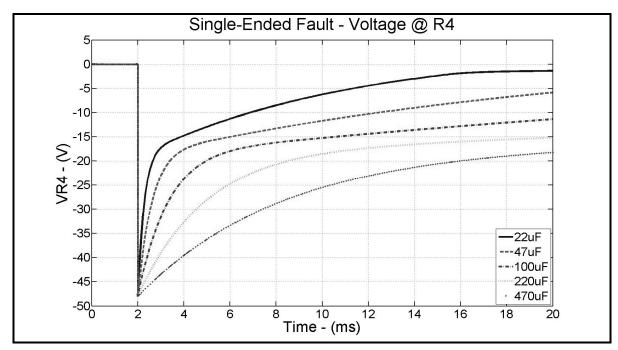

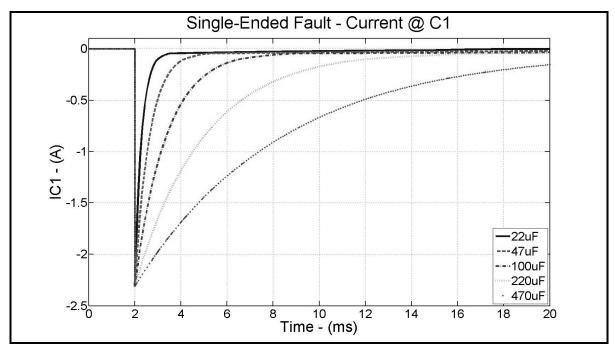

When SW1 is closed, -48 V appears instantaneously across bias resistor R4, as shown in Figure 6. As in the common-mode fault, input capacitor C1 discharges to the V- rail primarily through protection diode D12, but also through Q3 in series with D14. Additionally, in this mode, since the INpin initially remains near -48 V, current flows through Q3 in series with RG and D24, and through Q3 in series with RG, the base-emitter junction of Q2, and D22. For simplicity, we only describe the case in which C1 is connected to ground. The results are symmetrical if, instead, C2 is connected to ground. Once the IN- pin reaches the negative supply rail (assumed to be -15 V in the simulation), fault currents stop flowing through the IC and the remaining charge on C1 bleeds off through R4. As in the common-mode fault, this gives rise to the two time constants evident in Figure 6.

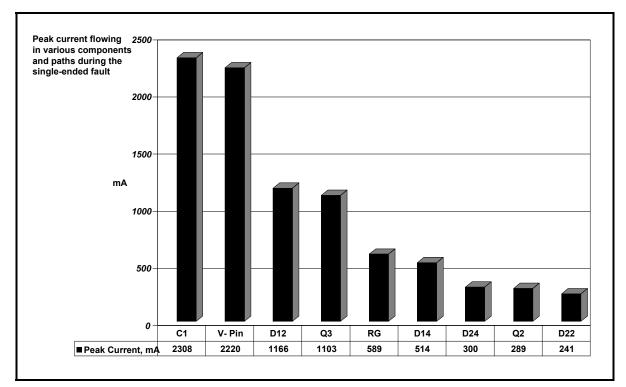

Figure 7 shows the levels of these currents. In the single-ended fault, the simulation predicts that the input capacitor will deliver a peak current of almost 2.4 A, almost all of which flows through the IC's negative supply pin (see Figures 7 and 8). Individual components within the IC are exposed to significant currents.

To generate the simulation data presented here, the gain resistor, RG, was set to  $10 \Omega$ . This corresponds to a high-gain condition (60 dB for a THAT 1510). RG plays a very important role here because its value determines the amount of current which flows through input transistor Q2 and protection diode D24. The higher the value of RG, the lower this current will be. For relatively high RG values (low preamplifier gains), the current path to the V- rail is mostly through protection diodes Q3 and D14, and the peak current is reduced. For single-ended faults, the highest currents are generated with the preamplese to the highest gain condition.

Figure 6. Voltage across bias resistor R4.

Figure 7. Current distribution during the single-ended fault.

Figure 8. Current through input capacitor C1.

#### 2.3. Differential Fault

A differential fault occurs when the two inputs are shorted to ground sequentially, with phantom power turned on, and without a microphone connected. At first glance, this fault might be considered a pair of singleended faults in sequence, but in the single-ended fault, one input is shorted while the other *remains open*. In this paper, the authors define the differential fault to occur when the second input is shorted after the first input has been shorted, and where the first input *remains shorted* during the second input's short.

Of course, the time between the two successive shorts will not necessarily follow any particular pattern. The first short need not persist long enough for its associated input capacitor to fully discharge before the second short occurs. However, the authors have found that the largest currents flow if the first input capacitor is completely discharged before the second input is shorted to ground. Accordingly, this is the case analyzed in detail.

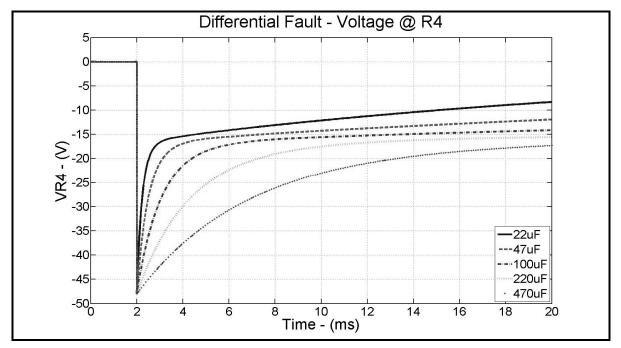

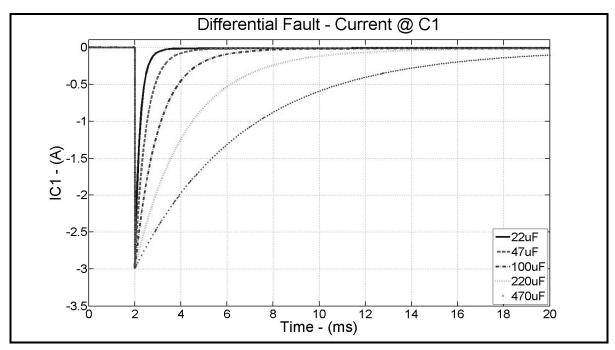

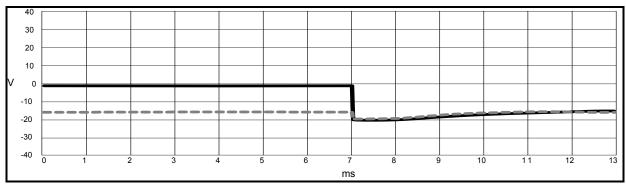

The simulation starts at time t = 0 with SW2 closed. Input capacitor C2 is connected to ground and contains no charge. At time t=2 ms, SW1 is closed, which shorts input capacitor C1 to ground. The results are equally valid for the other possibility, C1 connected to ground followed by C2.

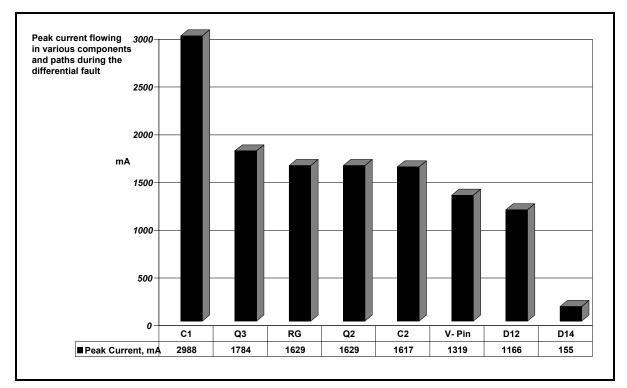

When the differential fault occurs, a -48 V transient appears across bias resistor R4 (Figure 9). Input capacitor C1 supplies high currents (Figure 10) as it discharges. As in the other fault mechanisms, the simulation shows that this current splits in several ways, flowing to the V- rail through a) protection diode D12; b) protection diodes Q3 and D14; c) Q3 in series with RG and D24; d) Q3 in series with RG, input transistor Q2, and protection diode D22; and e) through Q3, RG, Q2, and input capacitor C2. As with the other mechanisms, after the voltage across R4 becomes more positive than the V- supply (assumed here to be -15 V), the current through the IC drops to almost nothing, and the remaining charge bleeds off through R4. Figure 11 shows the associated fault currents through these paths.

In the simulation, approximately 40% (a little over 1.1 A) of C1's discharge current flows to the negative supply rail through ESD protection diode D12. The other 60% (almost 1.8 A) flows through reverse Vbe protection diode Q3. Only a small portion of Q3's current flows through ESD protection diode D14; the majority of current flows through gain resistor RG (set to 10  $\Omega$  in this simulation). The RG current flows through the base-emitter junction of Q2 and capacitor C2, and then to ground through SW2 (which is permanently closed). No current flows through protection diodes D24 and D22.

The differential fault produces a current loop between the inputs, formed by the reverse Vbe protection diode at one input, the gain resistor, the other input transistor, and the other (previously discharged and grounded) input capacitor. The loop current is primarily limited by the gain resistor, RG. As a result, the peak differential-fault current is a function of the gain setting of the microphone preamplifier when the fault occurs, and will be greatest at the highest gain.

#### 2.4. Fault Summary

Table 1 provides a summary of the simulated transient voltages and currents in each fault mode. The fault currents that flow through the protection diodes and input transistors are extremely high. In the authors' experience, no integrated devices are capable of withstanding such high currents without damage. Since phantom power faults are essentially inevitable, the most appropriate solution is to provide an external protection network to divert these currents safely around the IC.

|              | V peak |    | mA peak |      |      |      |     |     |    |      |      |     |      |      |

|--------------|--------|----|---------|------|------|------|-----|-----|----|------|------|-----|------|------|

| Fault        | R4     | R5 | C1      | C2   | D12  | D22  | D14 | D24 | Q1 | Q2   | Q3   | Q4  | RG   | V-   |

| Common Mode  | 48     | 48 | 1925    | 1925 | 1166 | 1166 | 720 | 720 | 0  | 0    | 720  | 720 | 0    | 3770 |

| Single-Ended | 48     | 23 | 2308    | 0    | 1166 | 241  | 514 | 300 | 0  | 289  | 1103 | 0   | 589  | 2220 |

| Differential | 48     | 14 | 2988    | 1617 | 1166 | 0    | 155 | 0   | 0  | 1629 | 1784 | 0   | 1629 | 1319 |

Table 1. Transient voltages and currents of the simulated fault conditions.

Figure 9. Voltage across bias resistor R4.

Figure 10. Current through input capacitor C1.

Figure 11. Current distribution during the differential fault.

# 2.5. Faults in Real World

Phantom faults can occur when:

- a) A user connects a microphone preamp input to a line level output, which has low output impedance and, sometimes, output protection diodes to the internal rails [1];

- b) The cable plug accidentally touches metal which is connected to ground (an equipment rack, a metal enclosure, the "sleeve" of a patch bay jack, etc.);

- c) A loose signal wire floating in a cable or connector due to damage or improper termination shorts to the shield ground, or a floating shield wire touches a signal contact;

- d) Metallic contact to ground is made to an exposed terminal block (e.g. barrier-strip) carrying microphone level signals;

- e) A TRS male plug with phantom energized on the tip and ring is plugged into a patch bay, making temporary contact with the grounded jack sleeve on its way in.

Due to their physical design, the exposed contacts of male TRS plugs are more likely to accidentally touch metal objects than the partially shrouded XLR contacts. Thus, TRS plugs are especially prone to causing phantom faults. However, XLR connectors are not immune to faults. When an XLR connector is plugged into a signal output, contact is made to the outside shield first due to the physical design of the connector. Contact is then made to each of the three signal pins. The angle of insertion and condition of the connectors (oxidation, exact length of the pin and the socket, width of the pin and socket, etc.) will vary, so the order in which the three signal pins make contact is unpredictable. Moreover, each individual contact may be intermittent or "bounce" as the connection is made. Thus, any of the described phantom faults can occur when devices are plugged together.

Some equipment provides "pseudo-balanced" or unbalanced outputs via XLR connectors. When a connection is made to the un-driven signal leg, a low or near-zero impedance connection is established between the microphone preamp input and ground, causing a single-ended fault. If the output is actively balanced, the differential fault occurs as the two signal legs are connected to the low impedance output nonsimultaneously. If the two legs make simultaneous contact, as suggested by Hebert/Thomas [1], this generates a common-mode fault. However, because common-mode faults require simultaneous connection, they seem the least likely to occur in the real world.

#### 3. PROTECTION SCHEMES

As described above, microphone preamplifiers can be exposed to very high currents when phantom power faults occur. During experimentation, it was found that many of the most commonly used protection schemes do not effectively protect ICs from these faults. In particular, differential faults can be very destructive when a preamplifier operates at high gain (low values for RG). The authors also discovered that some protection schemes introduce noise or distortion to the audio signal in the preamplifier front end. Some protection topologies are sacrificial in nature, most notably those using zener diodes. Zener diodes can protect an IC from damage by behaving as a fuse when the first fault occurs. However, this first fault can destroy the zener diodes, making them unable to provide protection against subsequent faults.

The following sections provide test results and discussion about the efficacy of many well-known protection schemes.

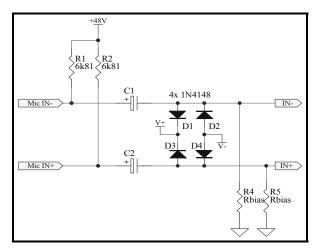

#### 3.1. 1N4148 Bridge to Rails

Figure 12 shows a common protection scheme using four 1N4148 diodes in a bridge configuration. This circuit attempts to clamp the input signal to the rail voltages, V+ and V- [3,4]. Unfortunately, these smallsignal diodes have too much forward voltage drop at the currents involved to steer enough current away from the IC. Moreover, the bridge concept (even if realized with power diodes) is ineffective against the input loop current generated during a differential fault.

Figure 12. 1N4148 bridge clamping the input signal to the rails. (Not recommended.)

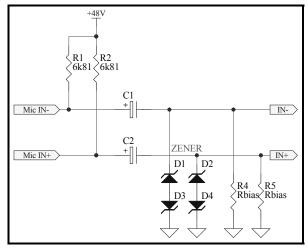

#### 3.2. Back-to-back Zener Diodes to Ground

Figure 13 shows a protection scheme using four diodes zener in a paired, back-to-back configuration, which attempts to clamp the input signal relative to ground [5]. In the authors' experience, this configuration will not reliably protect the IC unless the zener diodes are very large. <sup>1</sup>/<sub>2</sub>-watt and even 1-watt zeners do not survive the high currents (several Amperes) generated by some fault conditions. The situation is exacerbated because the zener diodes have significant voltage across them when they conduct. During the fault, they must dissipate significant power.

Moreover, this scheme may give a false impression that it is working because zeners will often fail as a short circuit. A single shorted zener will make the other zener it is connected to appear to the IC input as a diode. When this happens, the preamp may successfully pass low input-level signals, but will distort significantly at high levels.

One other consideration for the zener approach is that it may not offer protection when the unit is powered off. As shown in the simulations, one significant path for current to flow is to the negative rail. If the input is mis-connected to another preamp (powered up with phantom turned on), the zener diodes will only prevent the inputs from seeing signals up to their breakdown voltage. This might be enough to damage an un-powered IC.

Figure 13. Zeners back-to-back clamping the input signal to ground. (Not recommended.)

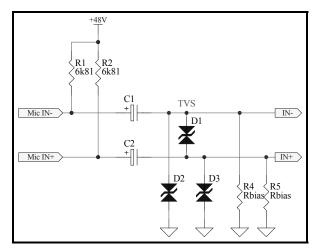

### 3.3. Bidirectional TVS

Figure 14 shows a protection scheme using 12-18 V bidirectional Transient Voltage Suppression (TVS) diodes. Because the TVS diodes are more rugged than typical ½- and 1-watt zeners, this scheme protects the IC in all three fault modes. However, in the authors' experience, TVS diodes have high intrinsic capacitance and substantial nonlinearities. These can interact with the source impedance to cause significant distortion to the signal. As a result, the authors do not recommend using TVS diodes directly across the preamp inputs for phantom fault protection.

Figure 14. Bidirectional TVS to ground and between the inputs. (Not recommended.)

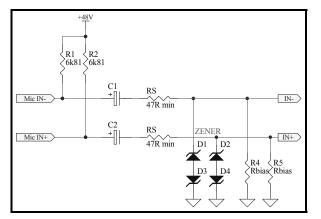

#### 3.4. Zeners + Series Resistors

Figure 15 shows a protection scheme using four zener diodes, in back-to-back configuration, with series resistors placed in front of the zeners to limit the fault currents. Jung and Garcia found that the minimum value for the series resistors should be approximately 47  $\Omega$  [6]. The resistance limits the current to a low enough value that the zeners survive the fault. However, the additional 94  $\Omega$  in series with the source compromises the noise performance of high-performance IC preamps [1].

A compromise might be sought by reducing the series impedance and increasing the wattage of the zener diodes. However, in the authors' experience, if the zeners are large enough to handle the fault currents, they increase distortion. Of course, if they are too small, they become sacrificial.

Figure 15. Zeners back-to-back to ground with series resistors. (Effective protection, but compromises noise.)

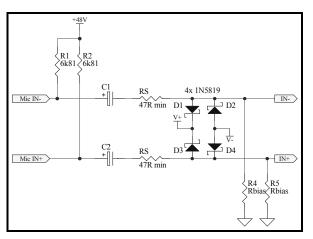

# 3.5. Schottky Diodes + Series Resistors

Figure 16 shows a protection scheme that uses Schottky diodes in a bridge configuration, clamping the input signal to the rails, with two resistors placed in front of the bridge to limit the fault current. The authors have found that minimum value of these resistors, required to protect against differential faults, is 47  $\Omega$ . Like the circuit of Figure 15, this compromises noise performance [1].

Moreover, Schottky diodes used in this way tend to introduce noise and DC offset due to diode leakage. While Hebert/Thomas once recommended this approach, the authors now recommend against it.

Figure 16. Schottky diode bridge clamping inputs to the rail. (Not recommended.)

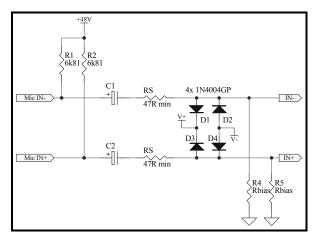

#### 3.6. 1N4004 Bridge + Series Resistors

Figure 17 shows a protection scheme using 1N4004GP<sup>1</sup> diodes in a bridge configuration, with series resistors placed in front of the bridge to limit the fault current. This circuit attempts to clamp the input signal to the power rails. The 1N4004 diodes are inexpensive and readily available.

The authors' experience is that this circuit will protect the part against all three fault modes, provided the series resistors are large enough. The 47  $\Omega$  resistors shown are effective, but they compromise noise performance at high gains. Previously, THAT Corporation had suggested this scheme in the past, with only 10  $\Omega$  series resistors. The authors have found that without more current limiting (extra resistance) this scheme will not protect the IC from differential faults.

Figure 17. 1N4004GP diode bridge clamping the inputs to the rail, plus input series resistors. (Effective, but compromises noise performance.)

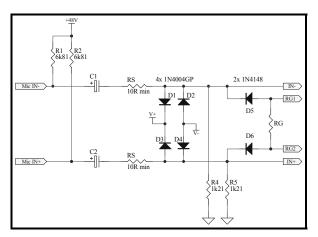

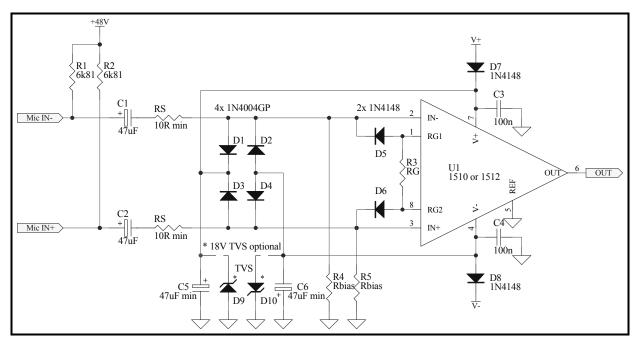

#### 3.7. Bridge + Series Resistors + B-E diodes

Table 1 reveals that very large currents flow through the input transistors, RG, and internal reverse Vbe diodes, Q3 and Q4 (Figure 2), during differential faults. Differential faults are most destructive to Q3 and Q4. Figure 18 shows a protection scheme which includes a pair of 1N4148 diodes to steer currents around Q3 and Q4 during faults. With the addition of these diodes, the current-limiting resistors at RS may be reduced to 10  $\Omega$

each, so noise performance is not unduly compromised. The authors have found that this protection scheme is effective against all three fault modes, and recommend it in preference to others.

Figure 18. Proposed protection scheme which incorporates two 1N4148 to steer the currents away from the base-emitter protection diodes.

#### 4. NEW PROTECTION SCHEME SIMULATION

After analyzing the three fault mechanisms, and considering the various protection schemes presented above, the authors focused on the circuit shown in Figure 18. This circuit was tested with a variety of microphone preamplifier ICs [2-6], and found to be both robust in protecting the ICs and 'transparent' in audio performance.

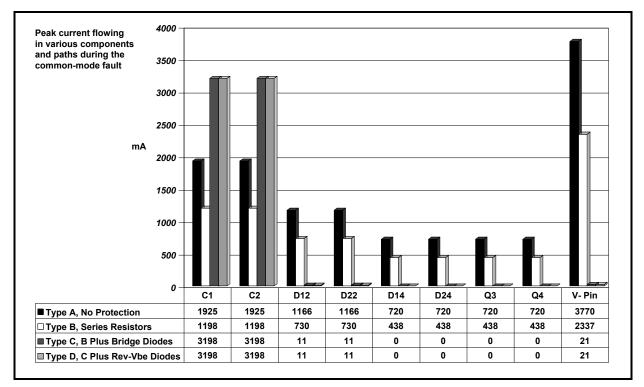

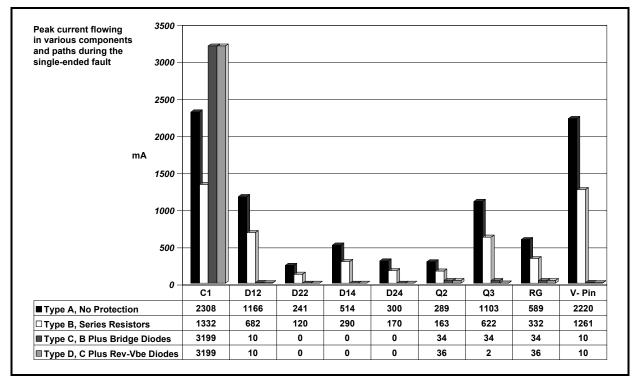

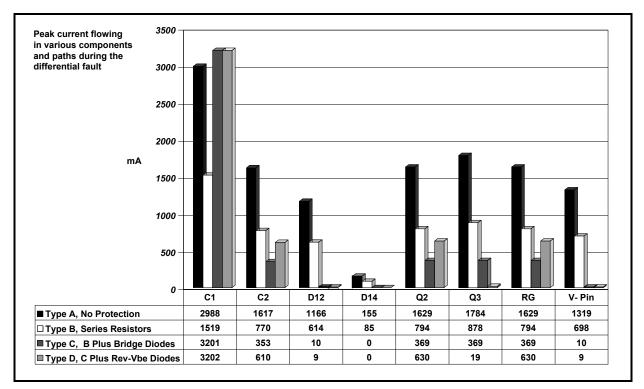

To understand why this circuit worked so well, the authors ran simulations of all three fault modes with different elements of the protection scheme shown in Figure 18. The results are shown in Figures 19, 20, and 21.

Each Figure shows a simulation for four different circuits, as follows:

A) the circuit of Figure 2;

B) the circuit of Figure 2, with two 10  $\Omega$  input series resistors (RS);

C) the circuit in B, plus the diode bridge (D1~D4) to the power supply rails; and

D) the circuit in D, plus base-emitter diodes (D5 and D6). This is the circuit shown in figure 18.

Other circuit parameters are:  $R4 = R5 = 1.21 \text{ k}\Omega$ ,  $RG = 10 \Omega$ , and V + / V = +/-15 V.

<sup>&</sup>lt;sup>1</sup> The "GP" indicates "glass passivated", which reduces leakage and avoids the problems mentioned above in connection with Schottky diodes.

Figure 19. Current distribution during the common mode fault for the circuits type A, B, C, and D.

Figure 20. Current distribution during the single-ended fault for the circuits type A, B, C, and D.

AES 127th Convention, New York, NY, USA, 2009 October 9–12

Figure 21. Current distribution during the differential fault for the circuits type A, B, C, and D.

The addition of 10  $\Omega$  input series resistors reduces fault currents, but 20  $\Omega$  (total) is not sufficient to protect the IC from differential faults. The experiments suggest that all preamplifier ICs will fail without some input series resistance. As well, although beyond the scope of this paper, the authors suspect that discrete designs will be similarly challenged by differential faults.

Adding the diode bridge to the rails appears (in the simulations) to provide signal clamping and current steering, but it also increases the fault current. The bridge steers voltages and currents away from the IC (and into the "stiff" negative supply rail) by reducing the impedance seen by the input capacitors while it clamps. This is why the discharge current is larger. However, by steering currents away from the IC, the diode bridge also significantly reduces the damaging currents flowing in the IC.

The external base-emitter diodes D5 and D6 are in parallel with internal diodes Q3 and Q4. They serve to reduce the current flowing in the internal protection diodes. D5 and D6 allow the input series resistors to be reduced from 47  $\Omega$  to 10  $\Omega$  while still protecting the part. This is important to maintaining a low noise floor. The equivalent input noise of a THAT1510 microphone preamplifier IC with 60 dB gain and its input shorted, is 1 nV/ $\sqrt{\text{Hz}}$ . With 10  $\Omega$  input resistors, the input noise is increased to 1.15 nV/ $\sqrt{\text{Hz}}$  – a compromise of 1.2 dB. With 47  $\Omega$  input resistors, the input noise goes up to 1.6 nV/ $\sqrt{\text{Hz}}$  – a compromise of 4.1 dB. Using typical 150  $\Omega$ microphone source impedance and 10  $\Omega$  resistors, the dynamic range is degraded by 0.4 dB. For the same source impedance and 47  $\Omega$  resistors, the dynamic range is compromised by 1.6dB. Therefore, by using 10  $\Omega$ resistors instead of 47  $\Omega$  the dynamic range is increased by 1.2 dB.

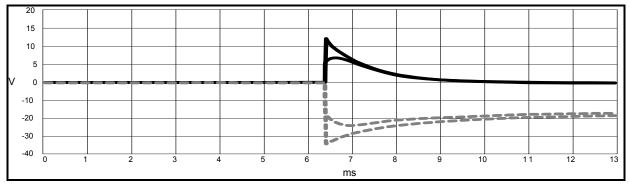

As shown in Figures 19~21, the differential fault is the most dangerous type due to the high currents flowing through the input transistors and base-emitter protection diodes. These high currents flow through the resistor gain RG, providing a convenient spot for non-invasive current measurement and evaluation of protection effectiveness.

Simulations, although helpful, can miss phenomenon witnessed in the real-world. For example, the data in Figures 19 through Figure 21 assumes the bridge diodes clamp the IC inputs exactly 0.6 V volts from the  $\pm/-15$

V power supplies (which are themselves modeled as perfect batteries). In practice, the power supplies are not batteries, and the clamping is not ideal.

In particular, simulator power supplies have low Thevenin impedance for both sinking and sourcing current. In the real world, most positive power supply regulators are only able to source current, and do a poor job of sinking it. The negative supply regulator will likely be a good sink but a poor source. Often, if a power supply output is driven past the regulated voltage by a phantomrelated fault, it has no means to correct the error and will go out of regulation. Consequently, the power supply will not instantly absorb the capacitor's transient discharge. In this case, the negative rail "moves" and the clamping voltage is no longer V-. Under these conditions the currents flowing through the IC can be significantly different from those predicted by the simulations.

# 5. REAL-WORLD TESTING

Given that the SPICE simulations presented above do not represent the real world of regulated power supply behavior, the authors measured the recommended circuit shown in Figure 18 on the bench. The results presented earlier show that the differential fault is the worst-case scenario, so the authors concentrated on that one. As well, the current flowing through the IC's frontend stage is essentially equal to the current flowing through the gain resistor RG and the internal baseemitter protection diodes. Thus, the differential voltage across RG permits indirect measurement of internal junction currents. Limiting transient currents through these junctions is the key to protecting against differential faults. To see how this circuit actually behaves, the authors observed various waveforms in the circuit. A digital oscilloscope was used to capture the waveforms.

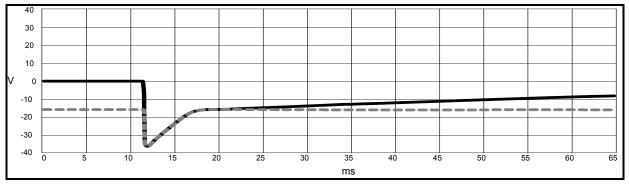

Figure 22 shows the voltage across the bias resistor R4 (solid trace) and the voltage at the V- rail (dashed trace) during a phantom power fault. Initially, the input voltage is zero and V- is -15 V. When the fault occurs, the input voltage is not clamped at V-, as predicted by the simulation, but drops to approximately -35 V, driven there by the discharge current in C1. Substantially the same behavior manifests regardless of the fault mode.

Initially it was suspected that the voltage to which the supply is driven would depend on the capacitance on the negative supply. But, after some investigation, the authors observed that the circuit was clamping to the bench power supply's regulator input voltage, which has a much larger filter capacitance than its output.

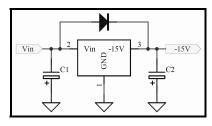

Figure 23 shows a typical three-terminal regulator with reverse polarity protection. The regulator output, typically an emitter follower, cannot source the current required to clamp transients. Regulator reverse polarity protection assures that transients more negative than the regulator input voltage get steered to the filter capacitance at the regulator's input. With the linear supply used in the tests, the unregulated supply voltage will determine the clamp voltage.

Other loads connected to the regulator can also absorb the transient. Uncontrolled, a phantom fault applied to the circuit of Figure 18 can corrupt the entire V- supply. The authors expected that this could damage the IC preamp, as well as other circuitry, unless it can tolerate the transient increase in supply voltage.

Figure 22. During the fault, in the circuit of Figure 21, the negative rail (dashed) follows the voltage across R4 (solid).

Figure 23. Simple representation of a bench power supply or three terminal regulator. Typically, C1>>C2.

One means of clamping the negative excursion is to add a bypass capacitor from the IC's V- pin to ground (the same might be used for V+ as well) to form a capacitive voltage divider. (See C5 and C6 in Figure 24.) During a fault, a portion of the input capacitor's charge is transferred to the bypass capacitor through the bridge protection diode (D2 or D4). Bypass capacitors give the energy in the input capacitors (C1 or C2) a less destructive path to ground.

But, in order to limit the negative supply transient to a safe level (perhaps -18 V), a large capacitor is required. The charge distributes based on the size of the bypass capacitor relative to the input coupling capacitor. To limit the voltage increase on the supply bypass capacitor to, say, 3V, the bypass capacitor must many times larger

than the input coupling capacitor. This is often impractical.

However, on the bench, the authors found, somewhat surprisingly, that the IC preamplifiers were not damaged by the brief negative supply transient to -35 V shown in Figure 22. Nonetheless, a large disturbance on the negative supply might damage other circuitry, and so should be at least isolated, if not eliminated altogether. Accordingly, the authors sought a means to isolate them from the -15 V supply and other circuitry.

In Figure 24, diodes D7 and D8 isolate the IC's V+ and V- pins from the power supply rails supplying the rest of the system. D7 and D8 are forward biased during normal operation, but reversed biased when a phantom power fault occurs or an external voltage source is applied to the preamplifier inputs (+48 V discharging from the output capacitors of an ac-coupled line output previously connected to a phantom power source, for example). The protection bridge (D1~D4) terminates on the IC side of the supply diodes D7 and D8, containing any overvoltage from faults to within the preamp system itself. A modest-sized bypass capacitor (C5 and C6, shown as 47  $\mu$ F) serves to absorb some of the charge during the fault, limiting the voltage excursion at the supply pins.

Figure 24. New protection scheme with diode-isolated rails (D7, D8) and bypass capacitors (C5, C6) to ground.

Figure 25 shows the IC input voltage at Rbias (solid trace) and the isolated V- pin voltage (dashed trace), with capacitor C6 = 0.1  $\mu$ F, during a phantom power fault on the Mic IN+. The voltage at the IC's IN+ pin drops to approximately -48V. Without a means to absorb the input capacitor's charge, V- tracks the input voltage. Figure 26 shows the voltage at IN+ and V- for C6 = 47  $\mu$ F. Note, of course, that if C1 and C2 are scaled, the transient peak will scale directly unless C6 is also scaled similarly. Partly for this reason, and considering low-frequency response versus typical preamplifier input impedances,

the authors recommend that the input coupling capacitors be no larger than 100  $\mu$ F. As shown in Figure 25, unless a sufficiently large bypass capacitor is used, during fault events the negative rail can be driven above the maximum rating for typical IC preamplifiers. While the authors' experience is that IC preamps seem to survive this abuse, this does raise concerns over reliability. One way to address this without requiring such large capacitance is to place a TVS diode across the rail as shown at D10 in Figure 24. Figure 27 shows the same voltages if an 18 V TVS is included at D10.

Figure 25. Isolation diodes without capacitors C5 and C6. Input voltage (solid) and isolated negative rail (dashed).

Figure 26. Voltage at IN+ (solid) and V- (dashed), for the circuit of Figure 24 as is.

Figure 27. Voltage at IN+ (solid) and V- (dashed), for the circuit of Figure 24 including 18 V TVS diode at D10;  $C6 = 47 \mu F$ .

Figure 28 shows the voltages across the 10  $\Omega$  gain resistor (solid traces) and the isolated V- pin (dashed traces) using 0.1  $\mu$ F and 47  $\mu$ F bypass capacitors at C6. With a 0.1  $\mu$ F bypass capacitor, the peak current flowing through RG is approximately 1.2 A. With a 47  $\mu$ F bypass capacitor, the RG current drops significantly to approximately 700 mA. This current can be reduced even further if larger capacitors and/or TVS are used. The use of bridge diodes, TVS devices, and capacitors, has been explored by others to protect sensitive low-voltage programmable gain amplifiers against phantom faults [7].

TVS devices, isolated in this way by their use on the power supply lines for the preamplifier do not contribute signal distortion. This makes them applicable, in contrast to the circuit of Figure 14, which is not recommended. It is also possible to share elements from the circuit of Figure 24 among several preamplifiers, isolating each individual input with its own bridge (and providing each input with individual D5 and D6), but sharing the supply isolation and bypass components. The authors consider this one of many areas for further investigation. It was found that bypass capacitor values should be at least equal to the value of Cin (C1 or C2, Figure 24), and ideally greater than two times Cin, to provide protection from common mode faults where the effective value of Cin is doubled.

To date, most of this work's experiments and simulations have been focused on faults based on shorting the inputs. These faults share the common feature of drawing the IC input pins negative, with consequences as discussed in this paper. While this is clearly a common cause of faults, another class consists of those where a source of phantom power is mistakenly connected to the input of a microphone preamplifier. The authors have not yet studied this class of fault sufficiently to reach any firm recommendations. However, at a minimum, similar protection against excessive positive input excursions and on the positive power supply, seems appropriate to guard against this category. For this reason, Figure 24 includes components symmetrically arranged towards positive excursions.

Figure 28. Differential fault. Voltages across the gain resistor (solid) and the isolated V- voltages (dashed), for 0.1µF and 47µF bypass capacitors.

#### 6. CONCLUSIONS AND SUGGESTIONS

This work presents three phantom-power-related fault mechanisms: common mode, open-circuit single-ended, and differential, and proposes a new protection scheme which works under a variety of conditions with minimal impact on noise performance.

Similar previously published works have focused on common mode faults, but the authors' observation is that differential faults are the most dangerous to an IC.

Many of the protection schemes in use today are ineffective at protecting the active elements against phantom power faults.

The proposed new protection scheme is more robust than previous recommendations, steers destructive currents away from the IC during fault conditions, and isolates the phantom menace from the rest of the system.

The authors have tested the proposed protection scheme exhaustively, but understand that there are numerous conditions and applications which were not covered in this work. Designers should consider these limitations and modify circuitry as they deem necessary.

#### 7. ACKNOWLEDGEMENTS

The authors thank THAT Corporation for encouraging and supporting this work. Also, the authors thank Les Tyler, Bob Moses, and Fred Floru for their discussions and suggestions, and David Lail for editing the figures.

#### 8. **REFERENCES**

- Gary K. Hebert and Frank W. Thomas, "The 48 Volt Phantom Menace," 110<sup>th</sup> AES Convention, Amsterdam, The Netherlands, 2001 May 12-15;

- [2] THAT1500 Series datasheet, Doc. 600031 Rev.05, http://www.thatcorp.com/datashts/1500data.pdf;

- [3] INA217 datasheet, SBOS247B, 06/02 Rev. 02/05, http://focus.ti.com/lit/ds/symlink/ina217.pdf;

- [4] INA163 datasheet, SBOS177D, 11/00 Rev. 05/05, http://focus.ti.com/lit/ds/symlink/ina163.pdf;

- [5] SSM2019 datasheet, Rev.0, 02/03, <u>http://www.analog.com/static/imported-files/data\_sheets/SSM2019.pdf;</u>

- [6] Walt Jung and Adolfo Garcia, "A Low Noise Microphone Preamp with a Phantom Power Option," Analog Devices Application Note, AN-242, 11/93;

- [7] Gries et al., "Protection Circuit for an Input Stage, and Respective Circuit Arrangement," Patent Application No.: US 2008/0007884 A1.